Press release in PDF format

Barcelona, September 21, 2023. After three and a half years of research, the European-funded Marenostrum Experimental Exascale Platform (MEEP) project has successfully concluded its mission of promoting innovation and collaboration in advanced platform development. MEEP has thrived as a cutting-edge platform designed to offer novel and reusable IPs tailored for FPGAs and ASICs. Emphasizing heightened productivity and adaptable frameworks, MEEP serves as a co-design testing ground for software and hardware developers, equipping them with valuable resources to delve into new architectural concepts, validate benchmark performance, and demonstrate future system concepts.

Embracing Open Possibilities

MEEP's relentless embrace of the European RISC-V architecture was central to its mission. RISC-V is an open standard instruction set architecture (ISA) that champions collaborative efforts and design autonomy. This alignment liberates MEEP from the confines of proprietary ISAs, symbolizing a paradigm shift towards innovation and shared evolution. The FPGA-based emulation capabilities are inherent to MEEP, illuminating the dynamic capacities of individual or multiple accelerators spanning nodes.

Unleashing the Accelerated Compute and Memory Engine Accelerator (ACME)

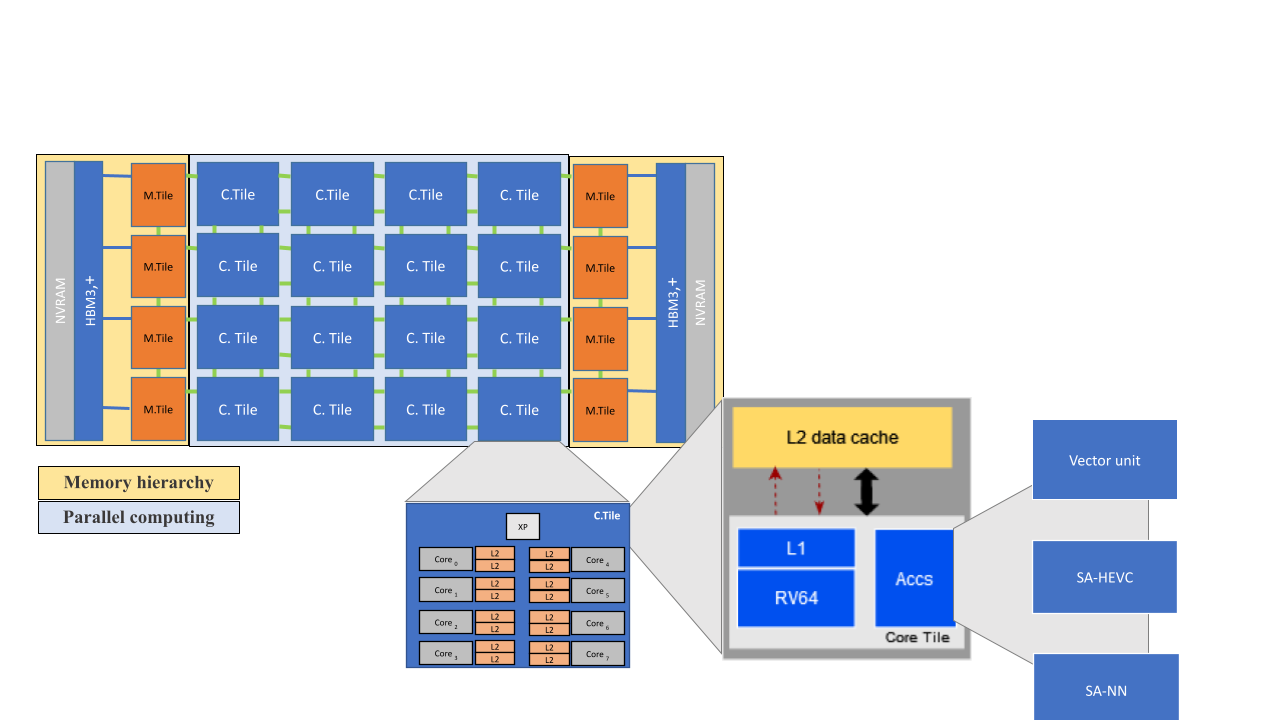

Accelerated Memory and Compute Engine (ACME), a self-hosted accelerator, is the core of the MEEP architecture. ACME holds immense potential for memory bandwidth-constrained tasks and compute-bound operations. Its architecture comprises two fundamental building blocks: a computational engine and a memory engine, working in tandem to optimize performance across different workloads. The computational engine handles data manipulation involving scalar and vector components, while the memory engine efficiently manages memory transactions and accesses, leading to energy savings and higher performance. The ACME architecture is underpinned by a multi-core RISC-V processor, tailored to handle scalar and vector instructions, and further integrates co-processors to enhance its performance capabilities.

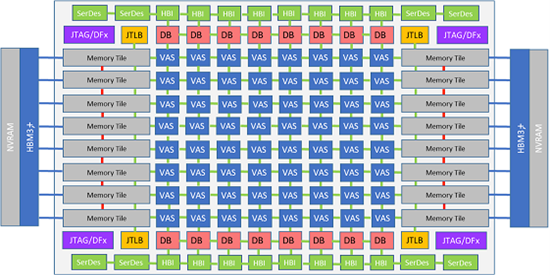

ACME architecture

The three accelerators —the Vector Processing Unit (VPU), the Systolic Array for video processing (SA-HEVC), and the Systolic Array for Neural Network (SA-NN)— share identical interfaces, simplifying control and programming. Furthermore, the uniform interfaces across these three vector accelerators streamline data flow control and programming in different operational modes (classic and acme) while laying the foundation for potential future accelerator exchanges. This demonstrates ACME's versatility as an accelerator capable of addressing various problem types, including vector architecture for HPC, SA-HEVC image and video processing, and SA-NN graph processing. Additionally, using systolic arrays has resulted in the development a customized vector extension, which has proven to enhance performance.

ACME accelerator and its microarchitectural details

The MEEP Project's Holistic Approach

MEEP's holistic approach involves a comprehensive collection of hardware IPs and software components harmoniously integrated within the FPGA-emulated system. FPGA devices provide the canvas for this intricate orchestration, resulting in the Emulated Accelerator ACME prototype. This prototype accommodates a wide range of high-performance computing applications, catering to dense and sparse workloads.

Navigating the Prototype

MEEP enables software and hardware designers to create an environment to explore the co-design space for future systems. MEEP enables pre-silicon validation of hardware IP and software development targeting new systems at a reasonable speed and higher scale than other techniques. In the case of mapping ACME to MEEP, one of the prototype's strengths is its ability to demonstrate different operation modes, e.g., with the offload mode, offering a familiar interface to users. Importantly, the ACME prototype is versatile enough to seamlessly implement both execution modes (offload and self-hosted), enhancing adaptability across diverse application scenarios.

MEEP is an exciting project broadly targeting the goals of European digital autonomy. MEEP is core semiconductor infrastructure demonstrating a new digital laboratory to support HPC semiconductor and systems development. ACME was used to demonstrate how to use MEEP as a co-design playground for pre-silicon validation and software development. We combine RISC-V accelerator development with fundamental FPGA IP to enable new hardware-software co-design. John Davis, Project Coordinator.

About MEEP project

The MEEP project (MareNostrum Experimental Exascale Platform) is a European-funded project with a budget of €10.3 million that started on January 1, 2020. Coordinated by the BSC, the project brings together three stakeholders: Barcelona Supercomputing Center (BSC, Spain), University of Zagreb, Faculty of Electrical Engineering and Computing (Zagreb, Croatia) and TÜBITAK BILGEM Informatics and Information Security Research Center (Gebze-Kocaeli, Turkey).

The MEEP project has received funding from the European High-Performance Computing Joint Undertaking (JU) under grant agreement No 946002. The JU receives support from the European Union's Horizon 2020 research and innovation programme and Spain, Croatia, and Turkey.