Lagarto Hun is the scalar core we selected for MEEP project; among other reasons because it is a BSC in-house RISC-V processor in which MEEP is contributing to its evolution.

Originally Lagarto Hun was a RV64IMA core with a 5 stages pipeline in order, supporting privileged ISA v1.11 [DRAC]. As a first improvement, and in direct collaboration with EPI and DRAC projects, we have added support for single and double precision floating point operations, becoming Lagarto Hun into a RV64IMAFD core, commonly named as RV64G for general purpose core.

FD Extensions support:

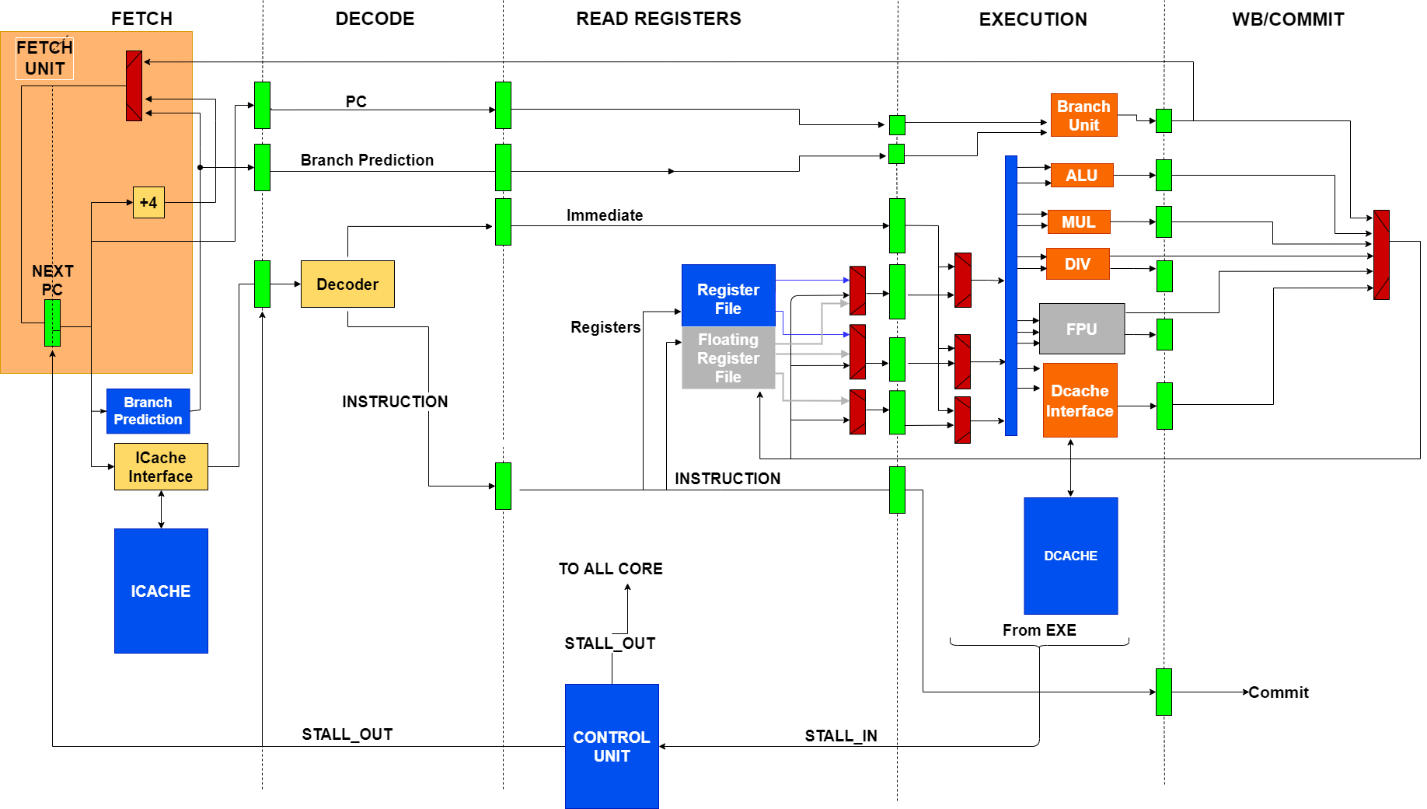

Adding support for F and D extensions required several modifications in the pipeline, as well as instantiating two new components: floating register file and Floating Point Unit (FPU). Figure 1 shows the microarchitecture of Lagarto Hun including the new modules highlighted in gray. The supporting of floating point operations required the following changes:

- Forwarding the floating point ISA instructions from the DECODE to the EXECUTION stage.

- Adding 32 floating point registers (according to the specifications [RISC-V ISA]).

- Adding floating point-unit in the EXECUTION stage.

- Adding control support for floating point operations, specially handling stalls from the EXECUTION stage.

- Expanding Control and Status Register file with floating-point control and status register.

- Enlarging the verification environment, by adding new tests (ISA, torture...).

Figure 1 Lagarto Hun RV64IMAFD (RV64G) block diagram microarchitecture

Figure 1 Lagarto Hun RV64IMAFD (RV64G) block diagram microarchitecture

C Extension support:

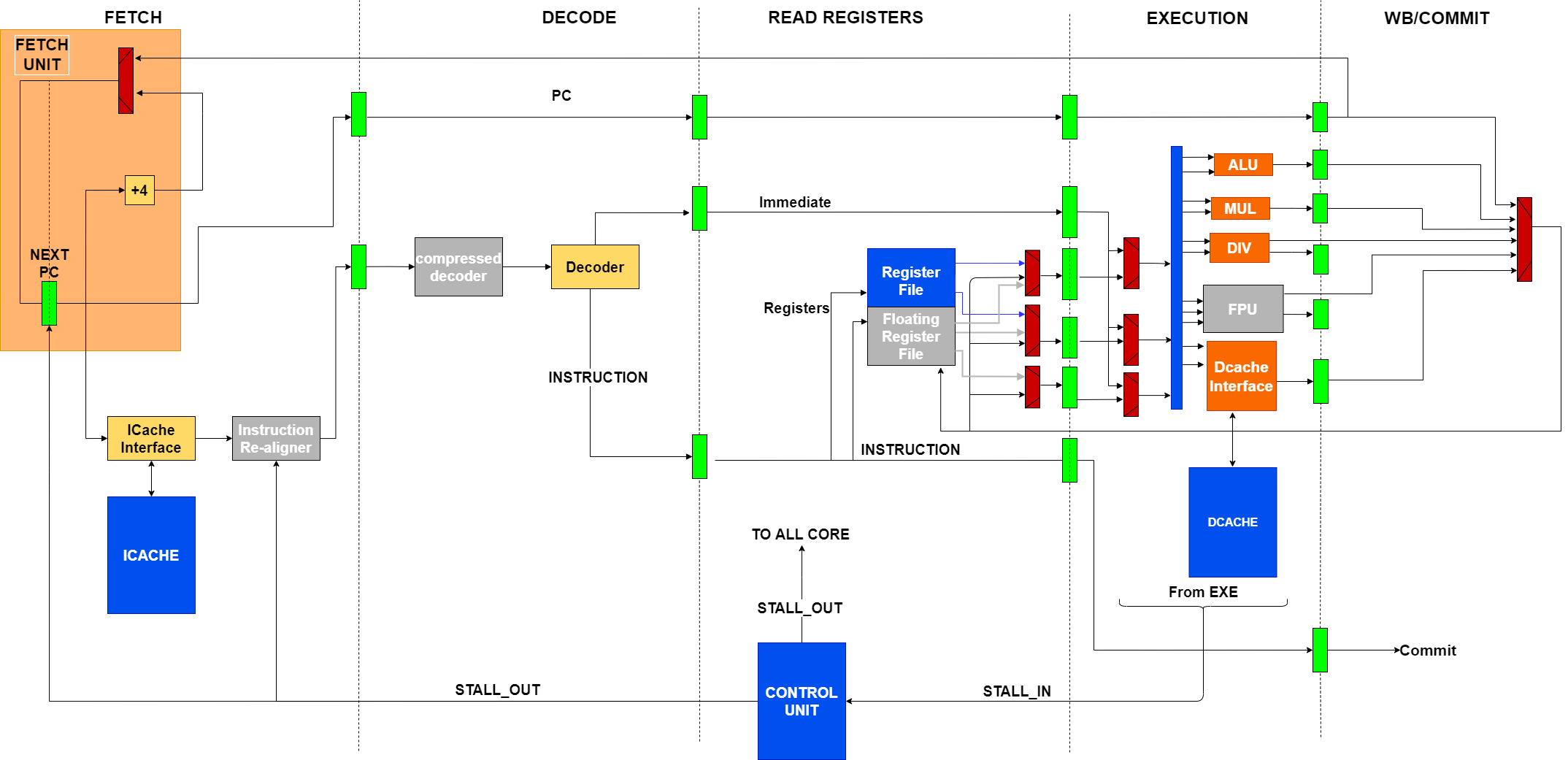

In a second phase, we have also added support for compressed instructions turning Lagarto Hun into an RV64GC core. Compress instructions reduces static and dynamic code size by adding short 16-bit instruction encodings for common operations instead of common 32-bit RISC-V instructions. In addition to that, these kinds of instructions are required for booting more complex operating system (OS) distributions out of the box, such as Fedora.

Figure 2 Lagarto Hun RV64GC block diagram microarchitecture

Figure 2 shows the microarchitecture of the final Lagarto Hun RV64GC core, with the new modules highlighted in grey: instruction re-aligner and compressed decoder.

To simplify the first development, we have disabled the branch prediction logic, which does not support compressed instructions. As a future work, it would be desirable to modify the branch predictor to support C-instructions as well.

The main modifications supporting this extension are related to the first two stages, FETCH and DECODE, which comprise the following changes:

- Forwarding C-instructions from the DECODE to the EXECUTION stage.

- Adding instruction re-aligner module that takes 32-bit aligned cache blocks and extracts the instructions to the next stage.

- Adding a compressed decoder, which expands compressed instructions into 32 bits. This prevents modifying the rest of the pipeline.

- Adding finite state machine (FSM) in the FETCH stage to stall fetching instructions when the 32-bit instruction cache block contains 2 instructions.

References:

[DRAC] https://drac.bsc.es

[RISC-V ISA] The RISC-V Instruction Set Manual Volume 1, Unprivileged Spec v. 20191213 https://riscv.org/technical/specifications/